Chip Gallery

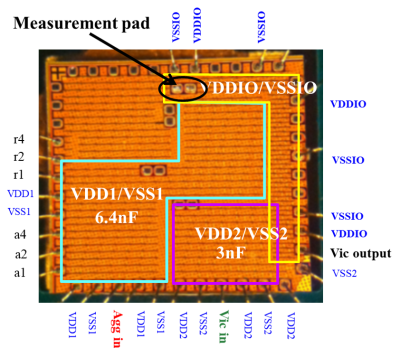

IC for power&signal integrity analysis (3)

[reference paper] Jingook Kim, Jongjoo Lee, Eunkyeong Park, and Youngwoo Park, “An Enhanced Statistical Analysis Method for I/O Links Considering Supply Voltage Fluctuations and Inter-Symbol-Interference“, IEEE Transactions on Components, Packaging and Manufacturing Technology, vol. 5, no. 8, pp. 1129-1141, Aug. 2015.

– Used for modeling of power supply induced jitter of switching buffers

– Fabricated with Dongbu MPW (110nm CMOS process), 2014.

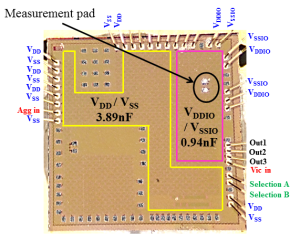

IC for power&signal integrity analysis (2)

[reference paper] Eunkyeong Park, Hyungsoo Kim, Jongjoo Shim, Yongju Kim, Yunsaing Kim, and Jingook Kim, “Analytical Calculation of Jitter Probability Density at Multi-Stage Output Buffers due to Supply Voltage Fluctuations“, IEEE Transactions on Electromagnetic Compatibility, vol. 57, no. 4, pp. 796-806, Aug. 2015.

– Used for analysis and measurement of power supply-induced jitter due to switching buffer

– Fabricated with Dongbu MPW (110nm CMOS process), 2014.

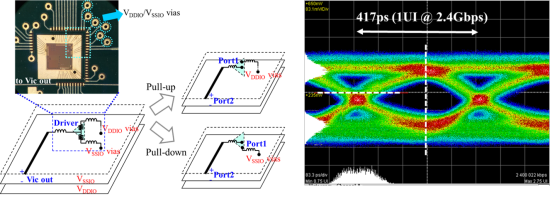

IC for power&signal integrity analysis (1)

[reference paper] Jingook Kim, Junho Lee, Sunki Cho, Chulsoon Hwang, Changwook Yoon, and Jun Fan, “Analytical probability density calculation for step pulse response of a single-ended buffer with arbitrary power-supply voltage fluctuations“, IEEE Transactions on Circuits and Systems I, vol. 61, no. 7, pp. 2022-2033, July 2014.

– Used for analysis and measurement of power supply noise due to switching buffer

– Fabricated with Samsung MPW (130nm CMOS process), 2013.