Chip Gallery

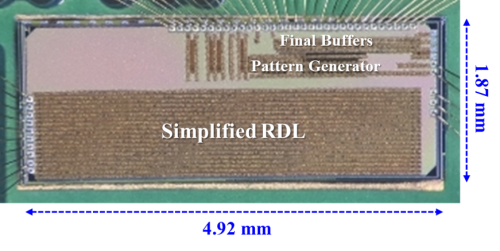

PAM3 SSO driver IC

[reference paper] Young-Sung Kwon and Jingook Kim, “Statistical Eye and BER Analysis for PAM3 Simultaneous Switching Outputs with Non-identical On-chip VDD and VSS Fluctuations“, accepted to IEEE Transactions on Circuits and Systems I: Regular Papers, 2025.

– PAM3 SSO driver IC for Statistical Analysis on Signal and Power integrity

– Fabricated with TSMC MPW (180nm BCD process), 2023.

Oscilloscope IC (2)

[reference paper] Kyunghoon Lee, Sangyeong Jeong, Wooshin Choi, Jung-Hwan Choi, and Jingook Kim, “Characterization and Application of Improved Oscilloscope IC for System Diagnosis of ESD and HPEM Effects“, IEEE Transactions on Electromagnetic Compatibility, vol. 66, no. 6, pp. 1804-1818, Dec. 2024.

– Oscilloscope IC (ver. 2) for on-system diagnosis

– Fabricated with TSMC MPW (180nm BCD process), 2023.

IC for EMI analysis of Wafer-Level Package

[reference paper] Jung Hoon Cho, Sangyeong Jeong, Jun-Bae Kim, Jeong Don Ihm, and Jingook Kim, “Prediction and Analysis of Radiated EMI from a Wafer-Level Package based on IC Source Modeling“, IEEE Transactions on Electromagnetic Compatibility, vol. 66, no. 1, pp. 281-292, Feb 2024.

– Used for analysis and measurement of EMI from Wafer-Level Package

– Fabricated with TSMC MPW (180nm BCD process), 2022.

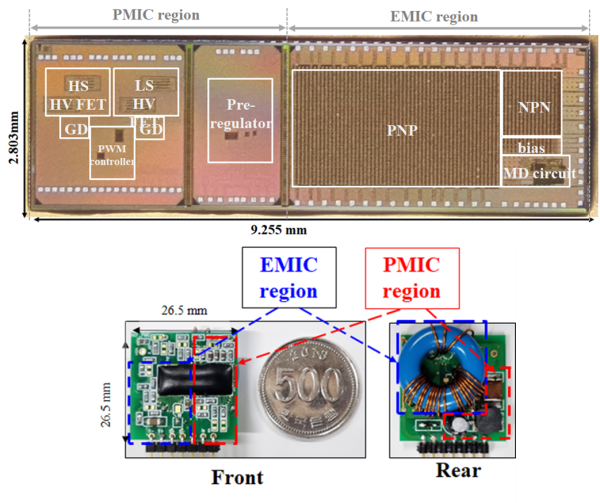

Electromagnetic Interference management IC (EMIC)

[reference paper] Sangyeong Jeong and Jingook Kim, “One-Chip Active EMI Filter with Integrated Buck Converter and Self-Malfunction Detection for CE Noise Reduction“, IEEE Transactions on Power Electronics, vol. 38, no. 11, pp. 13977 – 13987, Nov 2023.

– One-chip AEF IC + PMIC

– Fabricated with TSMC MPW (180nm BCD process), 2021.

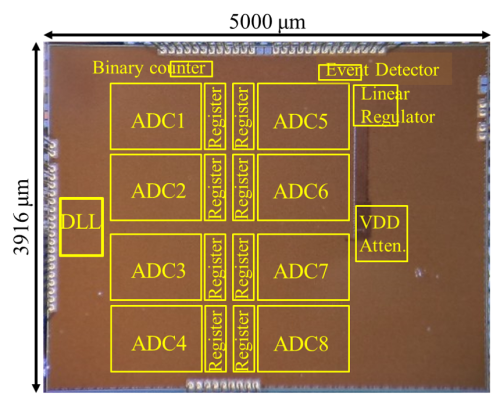

Oscilloscope IC

[reference paper] Zakirbek Mamatair Uulu, Jung Hoon Cho, Bumhee Bae, and Jingook Kim, “A Proposed On-die Oscilloscope for Monitoring of Power Noise waveform inside IC due to Transient Stress Events“, IEEE Transactions on Electromagnetic Compatibility, vol. 64, no. 2, pp. 429-442, April 2022.

– World-First oscilloscope IC for on-system diagnosis

– Fabricated with TSMC MPW (180nm CMOS process), 2020.

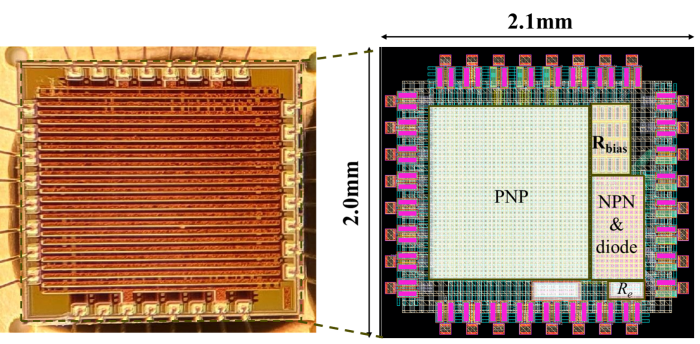

Active EMI filter IC

[reference paper] Sangyeong Jeong, Junsik Park, Jingook Kim, “A Customized Integrated Circuit for Active EMI Filter with High Reliability and Scalability“, IEEE Transactions on Power Electronics, vol. 36, no. 11, pp. 12631-12645, Nov. 2021.

– World-First IC for active EMI filter

– Fabricated with TSMC MPW (180nm BCD process), 2019.

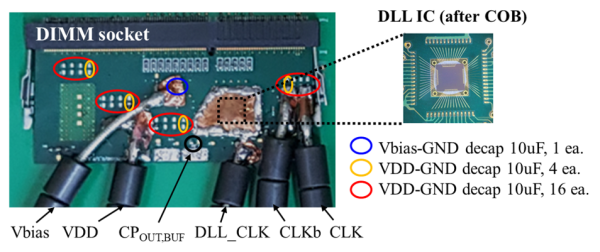

IC for measurement and analysis of ESD noise effects (2)

[reference paper] Myeongjo Jeong, Minchul Shin, Jinwoo Kim, Manho Seung, Seokkiu Lee, and Jingook Kim, “Measurement and Analysis of System-level ESD-Induced Jitter in a Delay-locked Loop“, IEEE Transactions on Electromagnetic Compatibility, vol. 62, no. 5, pp. 1840-1851, Oct 2020.

– Used for malfunction tests of Delay-Locked-Loop due to ESD noises

– Fabricated with M/H MPW (180nm CMOS process), 2016.

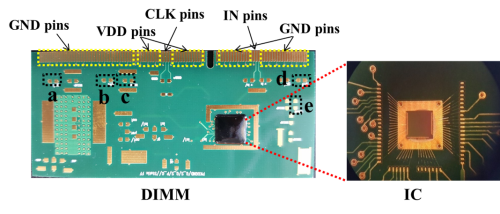

IC for measurement and analysis of ESD noise effects (1)

[reference paper] Myungjoon Park, Junsik Park, Joungcheul Choi, Jinwoo Kim, Seonghoon Jeong, Manho Seung, Seokkiu Lee and Jingook Kim, “Measurement and Analysis of Statistical IC Operation Errors in a Memory Module due to System-Level ESD Noise“, IEEE Transactions on Electromagnetic Compatibility, vol. 61, no. 1, pp. 29-39, Feb 2019.

– Used for malfunction tests of F/F register due to ESD noises

– Fabricated with M/H MPW (180nm CMOS process), 2015.

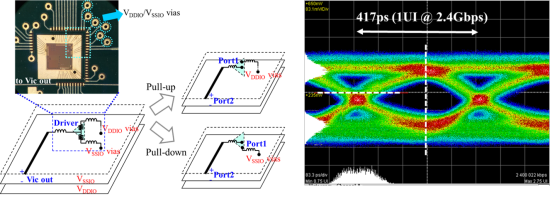

IC for power&signal integrity analysis (3)

[reference paper] Jingook Kim, Jongjoo Lee, Eunkyeong Park, and Youngwoo Park, “An Enhanced Statistical Analysis Method for I/O Links Considering Supply Voltage Fluctuations and Inter-Symbol-Interference“, IEEE Transactions on Components, Packaging and Manufacturing Technology, vol. 5, no. 8, pp. 1129-1141, Aug. 2015.

– Used for modeling of power supply induced jitter of switching buffers

– Fabricated with Dongbu MPW (110nm CMOS process), 2014.

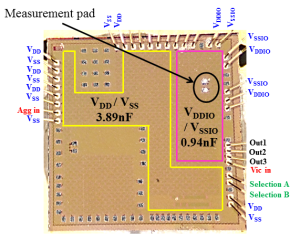

IC for power&signal integrity analysis (2)

[reference paper] Eunkyeong Park, Hyungsoo Kim, Jongjoo Shim, Yongju Kim, Yunsaing Kim, and Jingook Kim, “Analytical Calculation of Jitter Probability Density at Multi-Stage Output Buffers due to Supply Voltage Fluctuations“, IEEE Transactions on Electromagnetic Compatibility, vol. 57, no. 4, pp. 796-806, Aug. 2015.

– Used for analysis and measurement of power supply-induced jitter due to switching buffer

– Fabricated with Dongbu MPW (110nm CMOS process), 2014.