[reference paper] Myeongjo Jeong, Minchul Shin, Jinwoo Kim, Manho Seung, Seokkiu Lee, and Jingook Kim, “Measurement and Analysis of System-level ESD-Induced Jitter in a Delay-locked Loop“, IEEE Transactions on Electromagnetic Compatibility, vol. 62, no. 5, pp. 1840-1851, Oct 2020.

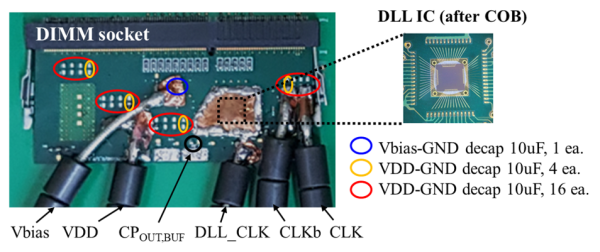

– Used for malfunction tests of Delay-Locked-Loop due to ESD noises

– Fabricated with M/H MPW (180nm CMOS process), 2016.